# CPT-R19 Card Red Phase Instruments TMS320F2810 DSP Controller Card For 590GV2, 689 and 809F Systems Technical Brief

September 2010 Manual Release 1.0 Card Version 1.0

Copyright © 2010

Creative Power Technologies P/L P.O. Box 714 MULGRAVE Victoria, 3170

Tel: +61-3-9543-8805 Fax: +61-3-9543-8802

Email: tech@creativepower.com.au

# **CPT-R19 Manual Revision History**

<u>CARD VERSION 1.0:</u> Initial Board for prototype purposes.

Release 1.0 – Initial Release of Manual.

i

# **Table of Contents**

| 1.0    | Overview of the CPT-R19                                                                                                                                                    | 1      |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1.1    | Digital I/O                                                                                                                                                                | 3      |

| 1.2    | Analog Inputs                                                                                                                                                              | 3      |

| 1.3    | Gate Drive Interface                                                                                                                                                       | 3      |

| 1.4    | Communications                                                                                                                                                             | 4      |

| 1.5    | On-card memory                                                                                                                                                             | 4      |

| 1.6    | Power Supply                                                                                                                                                               | 4      |

| 1.7    | JTAG/programming                                                                                                                                                           | 4      |

| 2.0    | Specifications                                                                                                                                                             | 5      |

| 2.1    | Controller DSP Section                                                                                                                                                     |        |

| 2.2    | Analog Inputs                                                                                                                                                              |        |

|        | 2.1 AC General Inputs                                                                                                                                                      |        |

| 2.3    | Digital I/O                                                                                                                                                                |        |

| 2.4    | Digital Inputs                                                                                                                                                             |        |

| 2.4    | 4.1 Interrupt Capable Digital Inputs                                                                                                                                       |        |

| 2.5    | Digital Outputs                                                                                                                                                            | 7      |

|        | 5.1 Open Collector Digital Outputs                                                                                                                                         | 7      |

|        | 5.2 3.3V-TTL Level Digital Outputs                                                                                                                                         |        |

| 2.6    | PWM Gate Drive Interface – EVB                                                                                                                                             |        |

| 2.7    | Communications Interface                                                                                                                                                   |        |

|        | 7.1 Serial Peripheral Interface – SPI                                                                                                                                      |        |

|        | 7.2 Serial Communication Interface – SCIA – TTL Level                                                                                                                      |        |

|        | <ul> <li>7.3 Serial Communication Interface – SCIA – RS-232 Level – Debug Port</li> <li>7.4 Serial Communication Interface – SCIA – RS-232 Level – DCE/DTE Port</li> </ul> | ه<br>۵ |

|        | 7.5 Serial Communication Interface – SCIA – RS-252 Level – BCE/BTE Fort                                                                                                    |        |

| 2.     | 2.7.5.1 SCIB - RS-232 Interface                                                                                                                                            |        |

|        | 2.7.5.2 SCIB - RS-422/RS-485 Interface                                                                                                                                     |        |

| 2.8    | JTAG                                                                                                                                                                       | 9      |

| 2.9    | Software                                                                                                                                                                   | 10     |

| 2.10   | General                                                                                                                                                                    | 10     |

| 2.11   |                                                                                                                                                                            |        |

| Append | ***                                                                                                                                                                        |        |

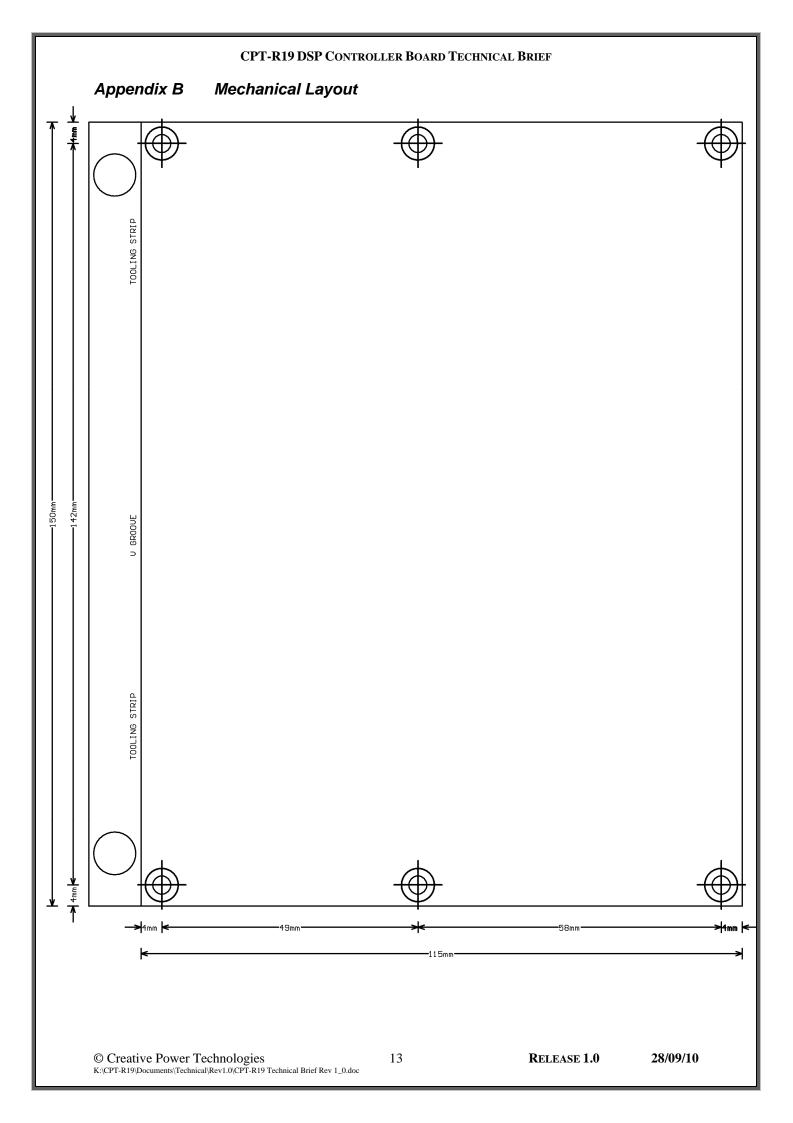

| Append | dix B Mechanical Layout                                                                                                                                                    | 13     |

|        |                                                                                                                                                                            |        |

ii

## **CPT-R19 DSP Based Inverter Controller**

#### 1.0 Overview of the CPT-R19

The CPT-R19 is a low cost, high performance DSP based inverter controller that has been designed to act as a central, high-speed, flexible controller for a new range of Red Phase Instruments products.

The board is based around a Texas Instruments TMS320F2810PBK DSP, which has been specifically developed for use in digital motor/motion control applications, and contains on-card all necessary functions for a complete standalone inverter control system.

The CPT-R19 card measures 150mm x 115mm.

#### On-card facilities include:

- TMS320F2810PBK DSP processor

- 64k x 16 Flash (128k x 16 Flash on TMS320F2811PBK)

- 1k x 16 OTP ROM

- 4k x 16 Boot ROM

- Software Boot Tables

- Standard Math Tables

- 18K x 16 Single Access RAM (SARAM) made up of:

- L0 and L1: 2 Blocks of 4K x 16 Each SARAM

- H0: 1 Block of 8K x 16 SARAM

- M0 and M1: 2 Blocks of 1K x 16 Each SARAM

- Serial Flash Memory with 1Mbit of non-volatile storage

- 1 off Power LED

- 4 off indication LEDs

- 4 off DIP switches

- 8 off open-collector digital outputs

- 2 off interrupt driven TTL-level digital inputs

- 8 off TTL-level individually configurable digital I/O bits

- 1 off SPI expansion interface, including chip selects

- 4 off precision reference ADC inputs (for calibration purposes)

- 12 off 12-bit 0-3V ADC inputs, with glitch filter and clamp diode protection

- 8 off complementary TTL-level gate driver PWM outputs, with fault interrupt and enable

- Reset/Power-On Circuitry

- Power supply to generate all on-card supplies

- Power supply operation from input +12VDC

The card also supports the following peripheral interfaces:

- JTAG interface

- 1 off clocked Serial Peripheral Interface (also enables external Flash reprogramming)

- 2 off selectable RS-232 serial interfaces

- 1 off TTL level serial interface

- 1 off isolated serial to RS232/RS422/RS485 interface

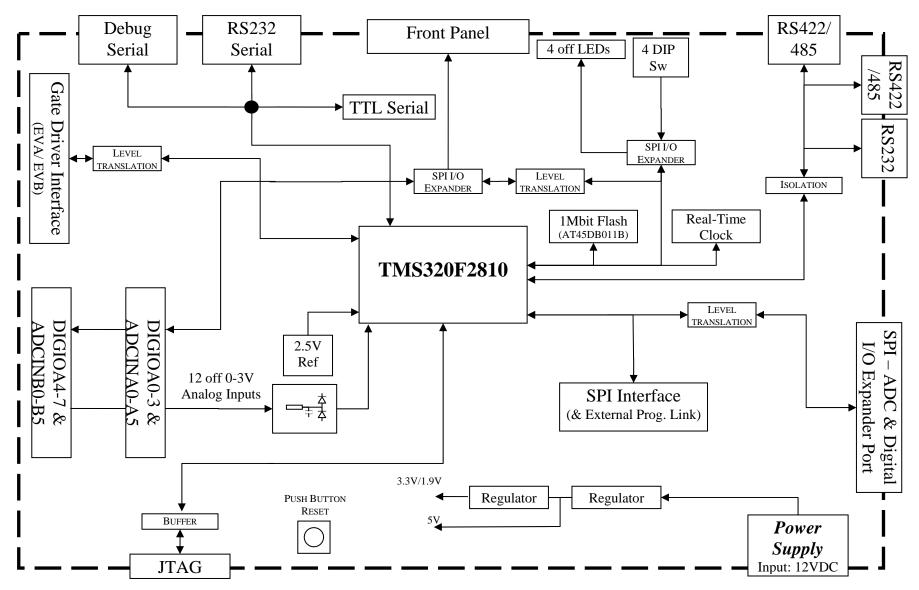

Figure 1-1 shows a functional block diagram of the CPT-R19 card, illustrating all major sections.

## CPT-R19 DSP CONTROLLER BOARD TECHNICAL MANUAL

Figure 1-1: Functional Diagram of CPT-R19 DSP Controller Board

## 1.1 Digital I/O

The CPT-R19 card supports up to 42 bits of digital I/O, consisting of 8 bits for local I/O, 8 bits of buffered open collector outputs, 2 interrupt driven digital inputs and 16 bits of buffered TTL level I/O.

The local I/O consists of 4 bits driving LEDs mounted on-card and 4 bits of DIP switch inputs.

The 8 off buffered open collector outputs are able to drive off-card relays or LEDs from a +5V or +12V supply. The 2 off interrupt driven digital inputs are TTL-level, zener clamped inputs that are level shifted to 3.3V-TTL before feeding into INT1 and INT2 on the DSP chip.

The CPT-R19 card supports a maximum of 19 bits of buffered digital I/O that can be configured as a bank of 11 digital outputs (Event Manager A & B PWM pins + PDPINT / Gate Reset lines) and 2 banks of individually configurable 4-bit SPI driven expansion ports. All of these bits are provided buffered with a level translation from the 3.3V-TTL of the DSP to a TTL level output.

The CPT-R19 card can support an off card SPI to Digital I/O expansion bus, which enables interfacing to over 100 individually configurable digital I/O bits.

All 3.3V-TTL digital I/O pins on the TMS320F2810 chip have the capability to operate in either "Digital I/O or "Peripheral I/O" mode. The header files for the CPT-R19 board select the default modes of operation for all of the pins on the board. The user is advised to refer to this file before programming their software code.

## 1.2 Analog Inputs

The TMS320F2810 DSP has 16 off ADC inputs that accept voltages in the range of 0-3V. The analog inputs are divided into two banks of 8 (ADCINA0-7 and ADCINB0-7). Each bank feeds into an 8 to 1 analog multiplexer with a sample and hold circuit. The outputs from the two sample and hold circuits are fed directly into a single 12-bit ADC Module. The ADC module is capable of interleaving ADC conversions between the two banks to achieve a "pipelined" conversion process. This reduces the overall time required for "simultaneous" conversions. The maximum total conversion time for each ADC unit is 80ns (with a 25MHz ADC clock).

The CPT-R19 analog inputs are configured to provide 4 off precision reference inputs for self calibration and 12 off filtered external inputs to the TMS320F2810.

The CPT-R19 card has on-card precision 2.5V and 1.25V references that should be used for calibration of the internal ADC. Each ADC bank has a 1.25V and 2.5V reference fed to channels 6 and 7 for calibration purposes. It is strongly recommended that the ADC be software calibrated for both gain and offset. Please consult the Texas Instruments documentation on the ADC converter for further information. *TMS320x281x DSP Analog-to-Digital Converter (ADC) Reference Guide*, Literature Number: *SPRU060D*.

The 12 off filtered analog inputs are separated into A and B channels that are available on separate 20-way IDC headers. Each input has a low pass or "glitch" filter and a diode clamp circuit before they are fed into the DSP. The board accepts 0-3V inputs for these circuits.

A 2.5V reference is also available on each of the 20-way header for use off-card. It is recommended that this reference be fed into an off-card op-amp circuit for external buffering rather than being used directly.

#### 1.3 Gate Drive Interface

The TMS320F2810 DSP supports 16 PWM channel outputs, made up of 6 complementary pairs (12 outputs) with programmable deadbands and 4 independent outputs generated by simple compare functions. The DSP chip has two independent Event Manager modules (EVA and EVB) and the PWM channels are evenly split between them. Dead band compensation must be software-calculated for the simple compare outputs.

The CPT-R19 is configured with one off 26-way header, which contains 8 PWM channel outputs that can be link selected to be either sourced from EVB, or split as 2 off complementary pairs (4 outputs) from each Event Manager. In addition the header contains gate fault signals fed to the corresponding Event Manager PDPINT\*

interrupt pin. This enables a DSP hardware interrupt trip to immediately occur on detection of a fault, thus disabling the PWM signals within 12 nanoseconds using hardware logic internal to the DSP. The card has pull-down resistors on the PWM outputs to ensure that they are left in a normally low state if either PDPINT\* fault signal is triggered. A gate reset signal is also provided on the header to enable the off-card gate drivers to be reset in the event of a fault.

#### 1.4 Communications

The CPT-R19 controller board supports three communication protocols: one off non-isolated 3.3V-TTL and two off non-isolated RS-232 serial communications interfaces (SCI), a 3.3V-TTL synchronous serial peripheral interface (SPI) and an isolated RS-232/422/485 serial communications interface.

The high-speed synchronous serial peripheral interface can be used to communicate to other computer systems. The interface can support either master or slave protocol, selected by software. The CPT-R19 has been provided with an SPI interface directly capable of reading from off-card SPI peripherals via the 26-way IDC header, **X9**.

The three external non-isolated serial communications interfaces all interface to SCIA on the DSP chip. Buffers with enable signals are provided for individual selection of the external interface. The RS-232 debug port, **X3**, is active by default and can be used to communicate to a terminal emulation program, to aid in program development.

#### 1.5 On-card memory

The CPT-R19 controller board supports 64k x 16bit of on-card Flash (128k x 16bit with the TMS320F2811), 18k x 16bit of SARAM and a 4k x 16 Boot ROM. Programs can be directly executed from RAM, via the JTAG interface or from Flash. By default, the card runs programs from the flash memory. Links are provided to enable RAM, SCI or SPI program operation.

In addition to the on-chip memory the CPT-R19 has a 1Mbit SPI interfaced Flash Memory chip for external data storage.

## 1.6 Power Supply

The standard CPT-R19 controller board operates from a nominal +12VDC. The board has on-card regulators that generate regulated +5V, +3.3V and +1.9V. These supplies are not isolated from the incoming +12V.

The isolated RS-232/422/485 interface is externally powered via **X14/X15** or the **X16** connector.

## 1.7 JTAG/programming

The CPT-R19 controller board has a JTAG interface for programming the DSP's Flash ROM or RAM. This port can also be used for emulator/debugging purposes using the Code Composer Studio JTAG Pod.

#### **Specifications** 2.0

#### Controller DSP Section 2.1

| Processor                      | Texas Instruments TMS320F2810 (optional TMS320F2811)                                                                           |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| On-card Memory                 | 64k x 16 Flash Memory (128k x 16 TMS320F2811)<br>18k x 16 RAM<br>4k x 16 Boot ROM<br>1k x 16 OTP ROM                           |  |

| Reset                          | 120ms hardware reset generated on-card from power up and supply failure. Can also be triggered via an on-card push button (S2) |  |

| Non-Volatile Memory<br>Storage | 1Mbit of memory storage using an SPI flash ROM chip Accessed via SPI interface on DSP                                          |  |

| Interrupts                     | 3 off masked external interrupts (XINT1, XINT2, XINT13/NMI) Support for 2 off PDPINT interrupts (on <b>X5</b> )                |  |

#### 2.2 **Analog Inputs**

| Number of Channels  | 16                                                    |       |

|---------------------|-------------------------------------------------------|-------|

| A/D Resolution      | 12 bits                                               |       |

| A/D Conversion Time | 80ns                                                  |       |

| Number of ADC's     | 1 (8 channels are multiplexed on-chip to form a bank) |       |

| Number of S/H units | 2 (each bank has one sample and hold unit             | t)    |

| Reference Voltages  | ADCINA6, ADCINB6                                      | 2.5V  |

|                     | ADCINA7, ADCINB7                                      | 1.25V |

#### AC General Inputs 2.2.1

|                     | 12 off 0-3V analog inputs with low pass filter capacitors |

|---------------------|-----------------------------------------------------------|

| Definition          | ADCINA0-5                                                 |

|                     | ADCINB0-5                                                 |

| Input Voltage Range | 0-3V maximum                                              |

| Dynamic Response    | Cut-off frequency >150kHz                                 |

| PCB Connections     | ADCINA0-5 on 16-way IDC header (X8)                       |

| PCD Connections     | ADCINB0-5 on 16-way IDC header (X7)                       |

#### Digital I/O 2.3

| Definition                           | 8 bits total                                                          |

|--------------------------------------|-----------------------------------------------------------------------|

| Definition                           | Digital I/O Expansion Port 0x07 addressable through the SPI Interface |

| Digital high input voltage threshold | 4.0V                                                                  |

| Digital low input voltage threshold  | 1.0V                                                                  |

| Interrupt Capable                    | Yes, Common Digital Interrupt Input to CAP3 on the DSP                |

| Digital I/O rated at                 | Source 3mA per bit, ABSOLUTE MAXIMUM                                  |

| Digital I/O rated at                 | Sink 8mA per bit, ABSOLUTE MAXIMUM                                    |

| PCB Connection                       | DIGIOA4-7 – 16-way IDC header ( <b>X7</b> )                           |

| red connection                       | DIGIOA0-3 – 16-way IDC header ( <b>X8</b> )                           |

#### 2.4 **Digital Inputs**

#### Interrupt Capable Digital Inputs 2.4.1

|                                      | 7 bits total                                                                                                                           |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|                                      | 2 off PDPINT* Gate Driver Interrupt Inputs (PDPINTA*, PDPINTB*)                                                                        |

|                                      | 2 off TTL-level External Interrupt Inputs (zener clamped) (XINT2, XINT3)                                                               |

| Definition                           | 1 off TTL-level External Interrupt Input (XINT1)                                                                                       |

|                                      | 2 off TTL-level Capture Port Inputs (CAP1, CAP6)                                                                                       |

|                                      | Note: Digital I/O Expansion Port 0x07 can be configured to be interrupt driven providing 8 additional indirect interrupt driven inputs |

| Digital high input voltage threshold | 3.85V                                                                                                                                  |

| Digital low input voltage threshold  | 1.65V                                                                                                                                  |

| Digital I/O rated at                 | ±24mA per bit, ABSOLUTE MAXIMUM                                                                                                        |

|                                      | PDPINTA* (GATE_FAULTA*),                                                                                                               |

| PCB Connection                       | PDPINTB* (GATE_FAULTB*) – 26-way IDC header ( <b>X5</b> )                                                                              |

| r CD Connection                      | CAP1 (ZX), XINT1 (INT1), CAP6 (SPI_INT*) – 26-way IDC header (X9)                                                                      |

|                                      | XINT2 (INT2), XINT3 (INT3) – 14-way IDC header (X2)                                                                                    |

# 2.5 Digital Outputs

# 2.5.1 Open Collector Digital Outputs

| Definition     | 8 bits total of Open Collector Digital Outputs (can be referenced to +5V or +12V) |

|----------------|-----------------------------------------------------------------------------------|

| Definition     | Digital Output Expansion Port 0x07 addressable through the SPI Interface          |

| PCB Connection | DIGIOB0-7 – 14-way IDC header ( <b>X2</b> )                                       |

# 2.5.2 3.3V-TTL Level Digital Outputs

| Definition               | GPIOF11, F14                                     |

|--------------------------|--------------------------------------------------|

| Digital outputs rated at | ±4mA per bit, ABSOLUTE MAXIMUM                   |

| PCB Connection           | GPIOF11 & F14 – 10-way IDC header ( <b>X10</b> ) |

# 2.6 PWM Gate Drive Interface – EVB

|                      | 1 off 8 PWM Outputs                                                                                                               |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                      | Link Selectable as:                                                                                                               |

| Definition           | a) All PWM Outputs sourced from Event Manager B or                                                                                |

|                      | b) 4 PWM Outputs sourced from Event Manager A and 4 from Event Manager B                                                          |

|                      | Configuration a) Event manager B has 8 PWM outputs consisting of –                                                                |

|                      | 3 independent complementary pairs (6 outputs) with programmable deadband generation                                               |

| PWM Outputs Event    | 2 gate drive outputs generated from two independent outputs, for which deadband compensation must be implemented in software      |

| Manager Explanation  | Configuration b) 8 PWM outputs consisting of –                                                                                    |

|                      | 2 independent complementary pairs (4 outputs) with programmable deadband generation from Event Manager B                          |

|                      | 2 independent complementary pairs (4 outputs) with programmable deadband generation from Event Manager A                          |

|                      | PDPINTA*, which when unmasked and activated, immediately disables the PWM outputs. Response time is ~12nsec after fault detection |

| Gate Fault Interrupt | PDPINTB*, which when unmasked and activated, immediately disables the PWM outputs. Response time is ~12nsec after fault detection |

|                      | The PWM signals are placed into a high impedance state and have on-card pull-down resistors                                       |

| Gate Reset           | Normally Low Gate Reset Signal                                                                                                    |

| Output Voltage       | 0-5V                                                                                                                              |

| PCB Connections      | 26-way IDC header ( <b>X5</b> )                                                                                                   |

## 2.7 Communications Interface

| Definition    | The TMS320F22810 has two off serial communications interface ports (SCIA and SCIB) and two off serial peripheral interfaces (SPI and McBSP) |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|               | SCIA is operated as either an RS-232 or a 3.3V-TTL level serial port                                                                        |

| Configuration | SCIB is configured as an isolated RS-232/422/485 serial port                                                                                |

|               | The SPI interface is available at both 3.3V and 5V-TTL levels with separate chip selects                                                    |

# 2.7.1 Serial Peripheral Interface – SPI

| Definition     | Four-pin serial peripheral interface (SPI) module. It is a high speed, synchronous serial I/O port that allows a serial bit stream of programmed length (one to sixteen bits) to be shifted into and out of the device at a programmable bit-transfer rate <b>DEFAULT MODE:</b> Configured as SPI Mode |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | 3 wire SPI mode (with independent chip selects)                                                                                                                                                                                                                                                        |

| Compatibility  | Available as non-buffered, non-isolated 3.3V-TTL Level signals on <b>X10</b>                                                                                                                                                                                                                           |

|                | Available as non-buffered, non-isolated 5V-TTL Level signals on <b>X9</b>                                                                                                                                                                                                                              |

| DCD Connection | 10-way IDC connector ( <b>X10</b> )                                                                                                                                                                                                                                                                    |

| PCB Connection | Also available on 26-way IDC header (X9)                                                                                                                                                                                                                                                               |

## 2.7.2 Serial Communication Interface – SCIA – TTL Level

| Definition          | Two-wire asynchronous serial port (UART) that supports a 16-level, receive and transmit FIFO for reducing servicing overhead. The receiver and transmitter are double buffered with separate enable and interrupt bits  DEFAULT MODE: 3.3V-TTL level serial connection, providing two pin serial communications for interface to an off-card 3.3V-TTL level to RS-232 translation card. This is necessary for interfacing to a standard PC serial port |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Isolation           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Communications Port | SCIA                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PCB Connections     | 4-way pin strip header with VDD and GND connections (X1)                                                                                                                                                                                                                                                                                                                                                                                               |

# 2.7.3 Serial Communication Interface – SCIA – RS-232 Level – Debug Port

| Definition          | Two-wire asynchronous serial port (UART) that supports a 16-level, receiver transmit FIFO for reducing servicing overhead. The receiver and transmitt double buffered with separate enable and interrupt bits  Default RS-232 Debug Port |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Isolation           | None                                                                                                                                                                                                                                     |  |

| Communications Port | SCIA                                                                                                                                                                                                                                     |  |

| PCB Connections     | 10-way IDC header ( <b>X3</b> )                                                                                                                                                                                                          |  |

#### 2.7.4 Serial Communication Interface – SCIA – RS-232 Level – DCE/DTE Port

| Definition          | Two-wire asynchronous serial port (UART) that supports a 16-level, receive transmit FIFO for reducing servicing overhead. The receiver and transmitted double buffered with separate enable and interrupt bits  Configurable as RS-232 in DCE or DTE mode through <b>LK5</b> |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Isolation           | None                                                                                                                                                                                                                                                                         |  |

| Communications Port | SCIA                                                                                                                                                                                                                                                                         |  |

| PCB Connections     | 10-way IDC header ( <b>X4</b> )                                                                                                                                                                                                                                              |  |

#### 2.7.5 Serial Communication Interface - SCIB

| Definition          | Two-wire asynchronous serial port (UART) that supports a 16-level, receive at transmit FIFO for reducing servicing overhead. The receiver and transmitter a double buffered with separate enable and interrupt bits  Configurable to support either RS-232 or RS-422/485 communication mod through a single UART. Both modes cannot operate simultaneously |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Communications Port | SCIB                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Configuration       | Only one of RS-232 or RS-422/485 can be loaded                                                                                                                                                                                                                                                                                                             |  |  |

| Isolation           | ACSL-6310 1000V isolation (Please consult the datasheet for this component for full isolation information)                                                                                                                                                                                                                                                 |  |  |

#### SCIB - RS-232 Interface 2.7.5.1

| Definition      | RS-232 connection, providing two pin serial communications for interface to a standard PC serial port |

|-----------------|-------------------------------------------------------------------------------------------------------|

| Compatibility   | DCE                                                                                                   |

| PCB Connections | 10-way IDC header, with pinouts to suit standard PC 9 pin serial port ( <b>X6</b> )                   |

#### 2.7.5.2 SCIB - RS-422/RS-485 Interface

| Definition      | Selectable RS-422/RS-485 connection, providing a multi-drop communications interface using a differential signal |  |

|-----------------|------------------------------------------------------------------------------------------------------------------|--|

|                 | <b>D</b> EFAULT: RS-422 mode only.                                                                               |  |

| Compatibility   | External shorting is required of the differential transmit and receive signals to operate in RS-485 mode.        |  |

| Bus termination | Linkable terminating resistor and capacitor across input channel (R112, C96)                                     |  |

| PCB Connections | Paralleled RJ45 and 8-way MOLEX connector, to allow daisy chain multi drop connection (X14, X15)                 |  |

#### 2.8 **JTAG**

| Definition     | DSP interface connection, which enables the TMS320F2810 to interface to a ICE to provide a real-time debugging environment |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Compatibility  | Compatible with IEEE 1149.1 standard for scan-based emulation                                                              |  |

| PCB Connection | 14-way IDC connector ( <b>X12</b> )                                                                                        |  |

## 2.9 Software

| Standard Support<br>Software | Monitor Program, standard library source code, sample programs |

|------------------------------|----------------------------------------------------------------|

|                              | Texas Instruments: Code Composer Studio V3.3 and above         |

## 2.10 General

| Physical Dimensions  | L: 150mm                                                                        |

|----------------------|---------------------------------------------------------------------------------|

|                      | W: 115mm                                                                        |

|                      | H: 50mm approx.                                                                 |

| Mounting Arrangement | 6 off 3.5 mm holes                                                              |

|                      | - please consult the mechanical layout diagram in the appendix for full details |

| Environmental        | -20°C – 75°C ambient operating temperature                                      |

|                      | 5% - 95% non condensing humidity                                                |

# 2.11 Power Supply

| Input Voltage Nominal               | 12V DC                                                                                              |  |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|

| Input Voltage Range                 | 8VDC – 20V DC                                                                                       |  |  |  |

| Standalone Input Current            | <b>TBD</b> (depending on the active sections within the DSP)                                        |  |  |  |

| Max Input Power                     | Approx. TBD ~8W                                                                                     |  |  |  |

| Supplies Generated on-card          | +12V (+12V) used for generating all on-card regulated power supplies                                |  |  |  |

|                                     | +12R (+12V) Filtered Power Supply (available on connector <b>X9</b> )                               |  |  |  |

|                                     | +5V_DIG (+5V) Digital Supply (filtered +5V_DIG_FLT and +5V_DIG_FLTB)                                |  |  |  |

|                                     | VDD / VCC (+3.3V) Digital                                                                           |  |  |  |

|                                     | AVDD (+3.3V) Analog DSP Supply                                                                      |  |  |  |

|                                     | VDDCORE (+1.9V) DSP Core                                                                            |  |  |  |

|                                     | AVCCCORE (+1.9V) Analog Section DSP Core                                                            |  |  |  |

|                                     | +2.5V Analog Reference (2.5V_OC off-card filtered reference)                                        |  |  |  |

| Isolated Comms Port<br>Power Supply | Supply is generated from either <b>X16</b> or <b>X14/X15</b>                                        |  |  |  |

| Input Power Connector               | 4 pin plug-in PCB Mounting Terminal Block with 2 off +12V and 2 off GND connections, ( <b>X13</b> ) |  |  |  |

| CPT-R19 DSP CONTROLLER BOARD TECHNICAL BRIEF |                   |             |          |

|----------------------------------------------|-------------------|-------------|----------|

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              | <b>Appendices</b> |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

|                                              |                   |             |          |

| © Creative Power Technologies                | 11                | RELEASE 1.0 | 28/09/10 |

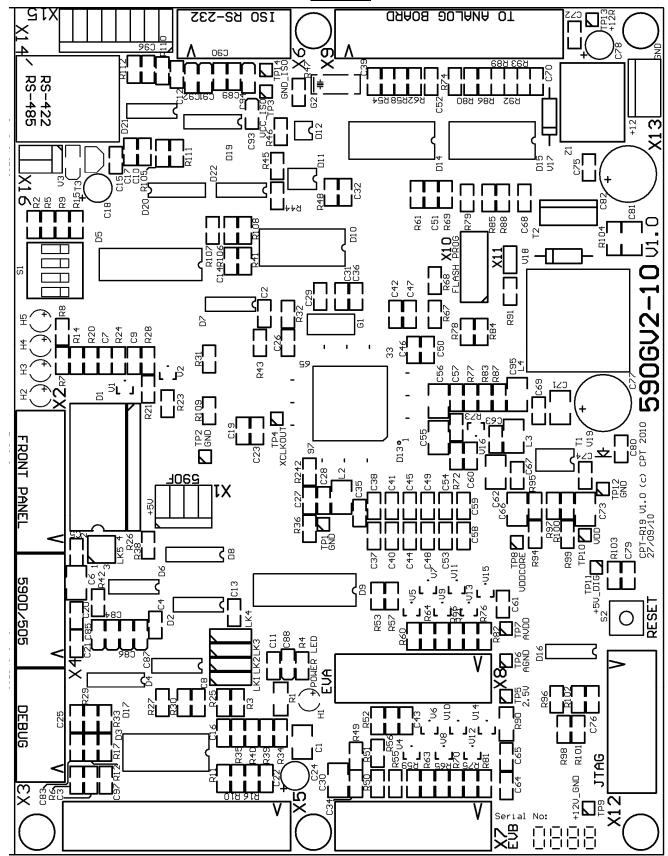

# Appendix A Component Layout

## **Top Layer**